# VSC7384 Data Sheet

## Stansted™ – 12-Port Layer 2 Gigabit Ethernet Switch

### **Features**

- 12 Gigabit Ethernet ports with nonblocking wirespeed performance

- Tri-speed (10/100/1000 Mbps) RGMII interfaces

- Support for both wire-speed automatic learning, and CPU-based learning

- 208 kB on-chip frame buffer

- Jumbo frame support

- Programmable classifier for QoS (Layer 4/Multimedia) into four classes of service

- 8,192 MAC addresses and 4,096 VLAN support (IEEE802.1Q)

- Per-port shaping, policing, and Broadcast and Multicast Storm Control

- IEEE802.1Q-in-Q nested VLAN support

- Full duplex flow control (IEEE802.3x) and half duplex back pressure

- Flexible link aggregation compliant with IEEE802.3ad

- Spanning Tree Protocol support (IEEE802.1D)

- Multiple Spanning Tree support (IEEE802.1s)

- Port-based Access Control (IEEE802.1X)

- IGMP, GARP, GMRP, and GVRP support

- Cost effective 4-pin serial CPU interface

- Selection between on-chip 8051 CPU, or off-chip 8-bit or 16-bit CPU for SNMP and Web-based management

# **General Description**

The Stansted is a full-featured, 12-port, Gigabit Ethernet switch-on-a-chip featuring several integrated management interfaces and support for both copper and optical PHYs using RGMII interfaces. The device provides nonblocking, wire-speed gigabit performance on all its ports. Web-based and SNMP management is made possible with the optionally enabled on-chip 8051 CPU, or through its performance-optimized 8-bit or 16-bit parallel interface.

In addition, less processor-intensive, managed operation is possible using a simple 4-wire serial interface.

Stansted has been optimized for SMB and desktop market segments, and does not require additional external memory.

Each device port is equipped with a Policer for ingress traffic control and a Shaper for egress traffic rate management.

The Stansted device also supports programmable higher layer classification and prioritization to enable enhanced Quality of Service (QoS) support for real time applications such as Voice over IP (VoIP).

# **Contents**

| Features                                              | 1  |

|-------------------------------------------------------|----|

| General Description                                   | 1  |

| Functional Overview                                   | 19 |

| Tri-Speed Gigabit MACs                                | 19 |

| Register Access                                       | 19 |

| Link Aggregation                                      | 20 |

| VLAN Support                                          | 20 |

| 802.1 Q-in-Q Support                                  | 20 |

| Quality of Service                                    | 21 |

| Flow Control                                          | 21 |

| Packet Forwarding Analysis                            | 21 |

| MAC Address Learning                                  | 22 |

| Shaping and Policing                                  | 22 |

| CPU Interfaces                                        | 23 |

| MII Management Interface                              | 24 |

| General Purpose I/Os                                  | 24 |

| Functional Description                                | 25 |

| Introduction – A Packet's Life in the Stansted Device | 25 |

| Switch Engine Operation and Congestion Control        | 26 |

| Priority Based Frame Discard                          | 27 |

|-------------------------------------------------------|----|

| Pausing Streams using Flow Control                    | 27 |

| Advanced Drop Mode                                    | 27 |

| Flow Control Mode                                     | 28 |

| MAC Features                                          | 29 |

| VLAN Features                                         | 30 |

| Frame Categorization                                  | 30 |

| Frame Priority Determination                          | 30 |

| Frame Class Determination                             | 33 |

| Policing                                              | 33 |

| General Policer                                       | 33 |

| Broadcast/Multicast Policer                           | 34 |

| Shaping                                               | 34 |

| Frame Analysis                                        | 34 |

| Tables in the Analyzer                                | 34 |

| Analysis Overview                                     | 35 |

| The MAC Table                                         | 36 |

| Automatic Learning from Incoming Packets              | 38 |

| Manually Manipulating MAC Table Entries using the CPU | 38 |

| Unlearning/Aging                                      | 38 |

| Frame Forwarding Decision                             | 38 |

| Exception Flags                                       | 40 |

| Categorizer Class                                     | 41 |

| Port Mirroring                                        | 41 |

| Jumbo Frames                                          | 41 |

| Early Transmission                                    | 42 |

| QoS and Jumbo Frames                                  | 42 |

| Flow Control and Jumbo Frames                         | 42 |

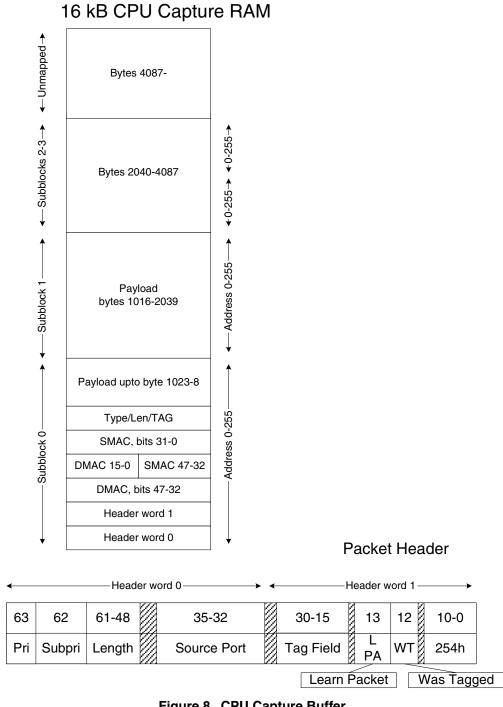

| CPU Packet Transmit and Receive                    | 44 |

|----------------------------------------------------|----|

| CPU Packet Transmission                            | 44 |

| CPU Packet Reception                               | 44 |

| CPU Based Learning                                 | 48 |

| iCPU                                               | 48 |

| Memory Organization                                | 49 |

| Pin Name Mapping                                   | 54 |

| External Memory Interface and Timing Configuration | 54 |

| Clock Frequency Select                             | 56 |

| Reset Options                                      | 56 |

| Interrupts                                         | 58 |

| Chip Register Access                               | 59 |

| Watchdog                                           | 60 |

| Timer 2                                            | 61 |

| The Serial Port                                    | 62 |

| General Purpose I/O                                | 65 |

| Dual Data Pointers                                 | 65 |

| Mailbox                                            | 65 |

| Debugging Features                                 | 66 |

| MII Management Bus                                 | 67 |

| Scan Operation                                     | 68 |

| Spanning Tree Protocol                             | 68 |

| Multiple Spanning Tree Protocol                    | 69 |

| onfiguration                                       | 70 |

| Command Interfaces                                 | 70 |

| Chip Register Space                                | 70 |

| SFR Register Space                                 | 71 |

| The Serial Interface                            | 73  |

|-------------------------------------------------|-----|

| SI Clock Select                                 | 74  |

| SI Configuration                                | 76  |

| The Parallel Interface                          | 76  |

| Reading Slow Registers                          | 78  |

| Interrupt Control                               | 78  |

| Register Addressing                             | 78  |

| 8-bit Data Bus Width                            | 79  |

| Minimum Software Requirements                   | 79  |

| Initialization Sequence                         | 80  |

| Port Mode Procedure                             | 81  |

| Register Overview                               | 82  |

| Chip Register Details                           | 87  |

| System Block Registers (Block 7)                | 87  |

| MAC Block Registers (Block 1)                   | 95  |

| Shared FIFO Block Registers (Block 1)           | 100 |

| Categorizer Block Registers (Block 1)           | 102 |

| Statistics Block Registers (Block 1)            | 108 |

| Detailed Counters Block Registers (Block 1)     | 109 |

| MII Management Bus Block Registers (Block 3)    | 114 |

| Memory Initialization Block Registers (Block 3) | 116 |

| Frame Arbiter Block Registers (Block 5)         | 117 |

| CPU Capture Block Registers (Block 4)           | 118 |

| Frame Analyzer Block Registers (Block 2)        | 119 |

| SFR Register Overview                           | 126 |

| General Purpose I/O SFRs                        | 126 |

| Dual Data Pointer SFRs                          | 127 |

| Memory Access Control SFRs                      | 129 |

| Watchdog SFRs                                   | 130 |

| Additional Timer Related SFRs             | 131 |

|-------------------------------------------|-----|

| Chip Register Access SFRs                 | 135 |

| Other SFRs                                | 137 |

| Signal Description                        | 138 |

| Signal List By Function                   | 138 |

| Signal List by Ball Number                | 147 |

| Signal List by Signal Name                | 152 |

| Electrical Specifications                 | 157 |

| Operating Conditions                      | 157 |

| Maximum Ratings                           | 157 |

| Power Sequencing                          | 158 |

| DC Characteristics                        | 158 |

| Clock Signal                              | 158 |

| RGMII and MII Management                  |     |

| iCPU, SI, JTAG, and Other Control Signals | 159 |

| Current Consumption                       | 160 |

| Typical Current Consumption               | 161 |

| Power Dissipation                         | 161 |

| AC Characteristics                        | 162 |

| Clock Timing                              | 162 |

| Reset Timing                              | 162 |

| RGMII (10/100/1000 Mbps)                  | 163 |

| MII Management                            | 165 |

| Serial CPU Interface                      | 166 |

| Parallel CPU Interface                    | 168 |

| iCPU External Memory Interface            | 171 |

| JTAG                       | 180 |

|----------------------------|-----|

| Design Guide               | 182 |

| Power Supplies             | 182 |

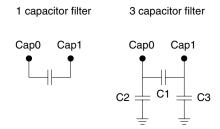

| Power Supply Decoupling    | 182 |

| PLL                        | 182 |

| PLL Supply Filtering       | 182 |

| PLL Loop Filter Capacitor  |     |

| PLL Inputs                 |     |

| GPIO                       | 183 |

| External Pull Resistors    | 184 |

| Interfaces                 | 184 |

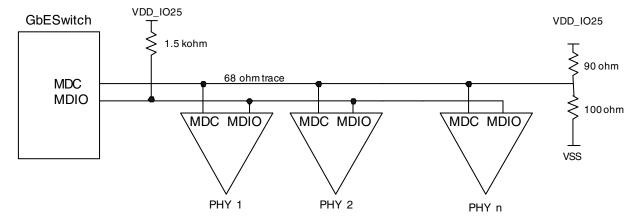

| MII Management             | 184 |

| Parallel CPU Interface     | 185 |

| Serial CPU Interface       | 185 |

| JTAG Interface             | 185 |

| MAC Interface              | 186 |

| Termination Considerations | 186 |

| iCPU Flash Access          | 187 |

| Other Design Information   | 187 |

| Signal Reference Plane     | 187 |

| Reference Clock            |     |

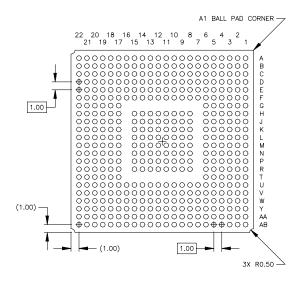

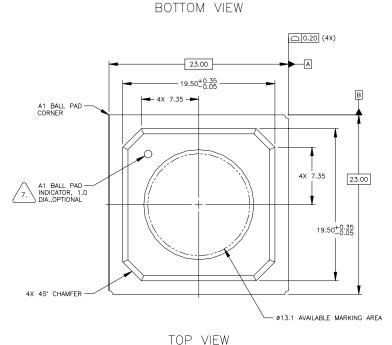

| Package Information        | 188 |

| Package Drawing            | 189 |

| Thermal Specifications     | 190 |

| Moisture Sensitivity       | 190 |

8 of 196

| Design Considerations                                  | 191       |

|--------------------------------------------------------|-----------|

| Incoming Pause Frames are Ignored for Egress-Congested | Links 191 |

| Issue                                                  | 191       |

| Implications                                           | 191       |

| Workaround                                             | 191       |

| Status                                                 | 191       |

| BC/MC Storm Control Drops Too Many Frames              | 192       |

| Issue                                                  | 192       |

| Implications                                           | 192       |

| Workaround                                             | 192       |

| Status                                                 | 192       |

| Ordering Information                                   | 193       |

| Standard References                                    | 194       |

| Ports                                                  | 194       |

| <b>Abbreviations</b>                                   | 194       |

# **Figures**

| Figure 1. Block Diagram                                                       | 19          |

|-------------------------------------------------------------------------------|-------------|

| Figure 2. The Life of a Packet                                                | 25          |

| Figure 3. Shared Packet Pool                                                  | 26          |

| Figure 4. Categorizer Priority Assignment Flow Chart                          | 32          |

| Figure 5. Frame Analysis                                                      | 35          |

| Figure 6. Hash Key Calculation                                                | 37          |

| Figure 7. Aggregation Example                                                 | 39          |

| Figure 8. CPU Capture Buffer                                                  | 46          |

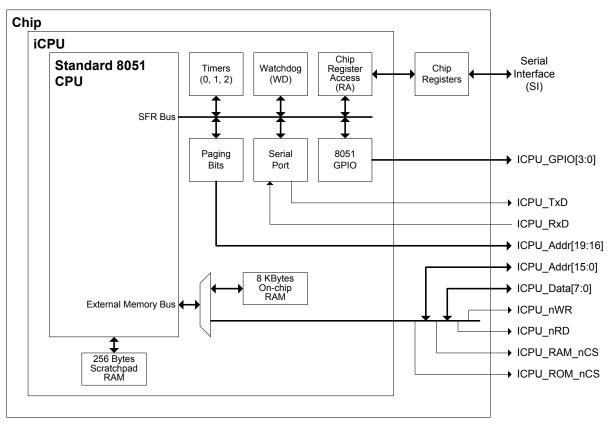

| Figure 9. iCPU Block Diagram                                                  | 48          |

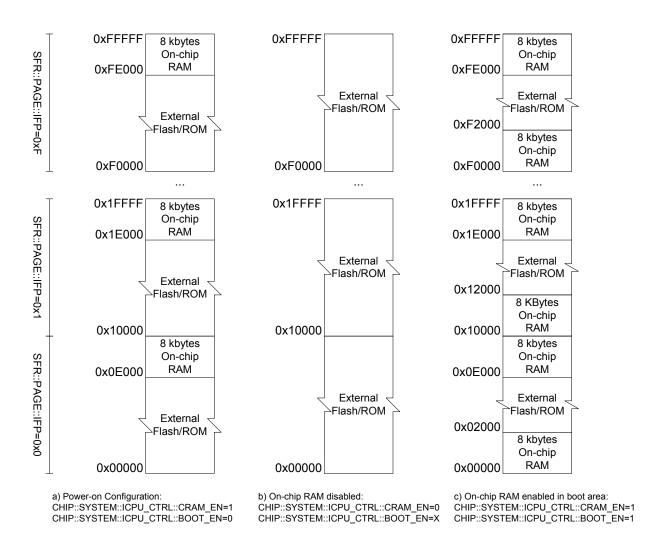

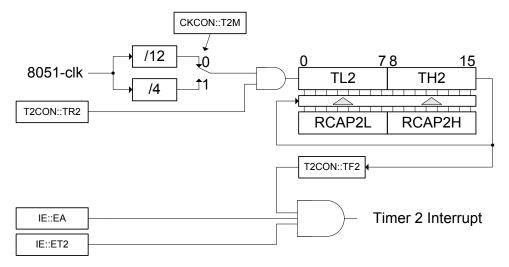

| Figure 10. Three Possible Program Memory Layouts for Program Memory Reads     | 51          |

| Figure 11. Data Memory Accesses with the On-Chip RAM a) Mapped In and b) Mapp | ed Out . 53 |

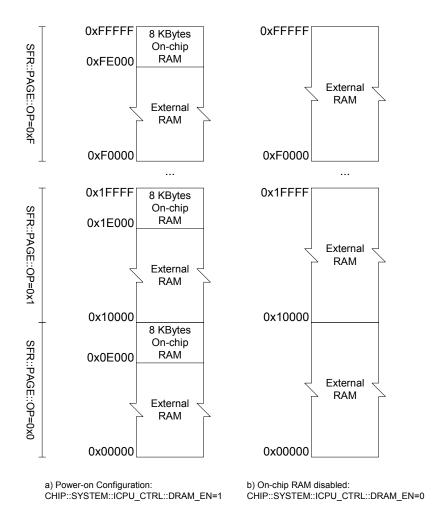

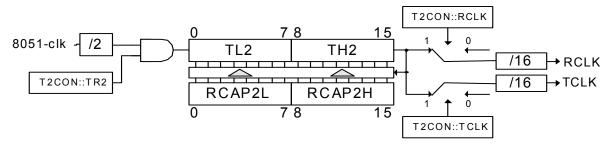

| Figure 12. Timer 2 as Timer/Counter with Auto-Reload                          | 61          |

| Figure 13. Timer 2 as Baud Rate Generator                                     | 62          |

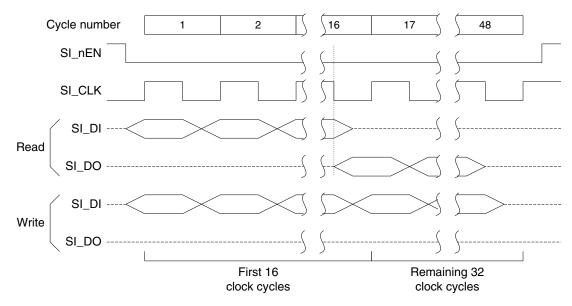

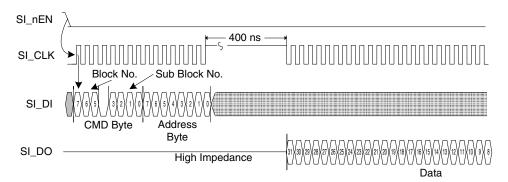

| Figure 14. Serial Interface Communication Sequence                            | 73          |

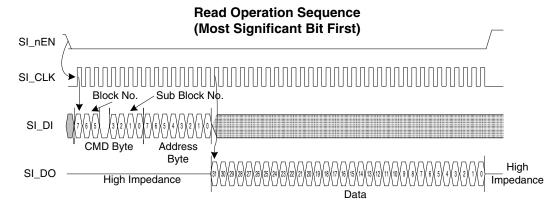

| Figure 15. SI Read Operation Sequence (Low Clock)                             | 74          |

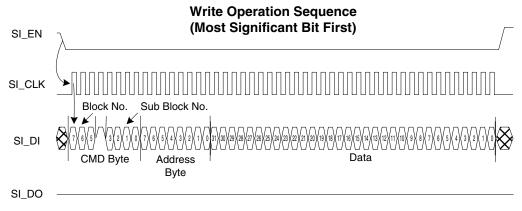

| Figure 16. SI Write Operation Sequence (Low Clock)                            | 74          |

| Figure 17. SI Read Operation with Clock Pause                                 | 75          |

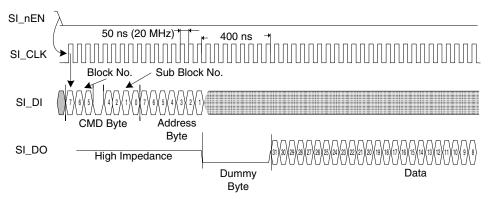

| Figure 18. SI Read Operation with Dummy Byte                                  | 75          |

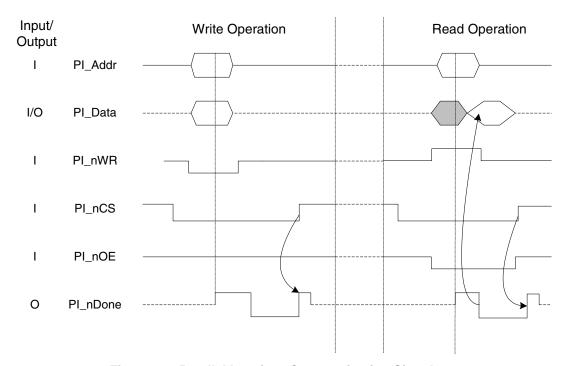

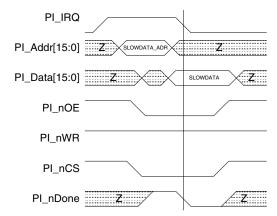

| Figure 19. Parallel Interface Communication Signals                           | 77          |

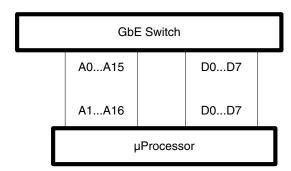

| Figure 20. 8-bit Data Bus Width                                               | 79          |

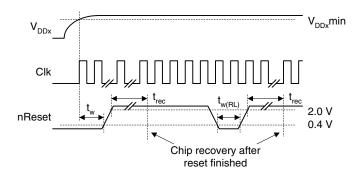

| Figure 21. nReset Signal Timing Parameters                                    | 162         |

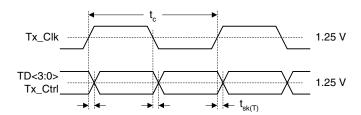

| Figure 22. RGMII Transmit Waveforms                                           | 163         |

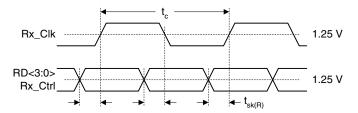

| Figure 23. RGMII Receive Waveforms                                            | 164         |

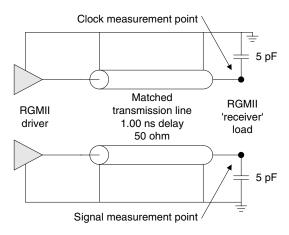

| Figure 24. RGMII Test Circuit                                                 | 165         |

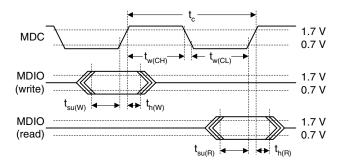

| Figure 25. MII Management Waveforms                                           | 166         |

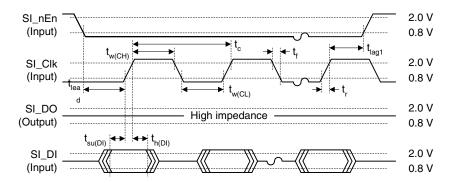

| Figure 26. SI Input Data Waveform                                             | 167         |

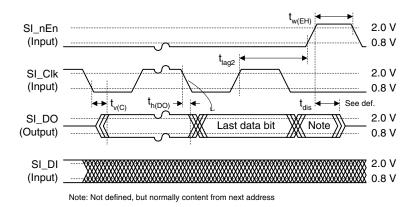

| Figure 27. SI Output Data Waveform                                            | 167         |

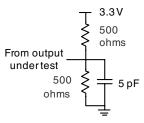

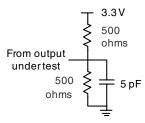

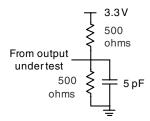

| Figure 28. Test Circuit for Signal Disable Test                               | 168         |

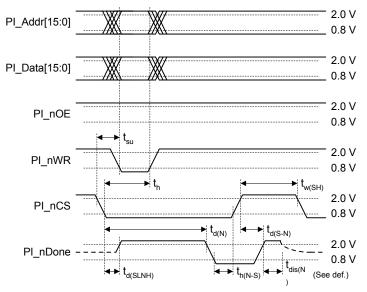

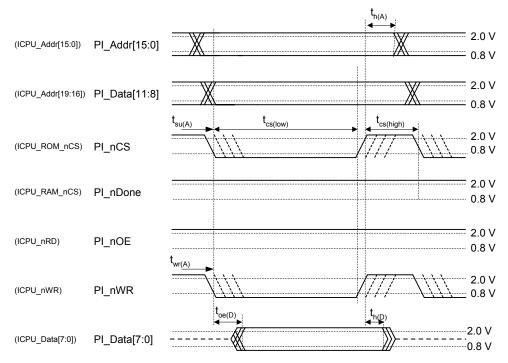

| Figure 29. PI Write Cycle (Input)                                             | 169         |

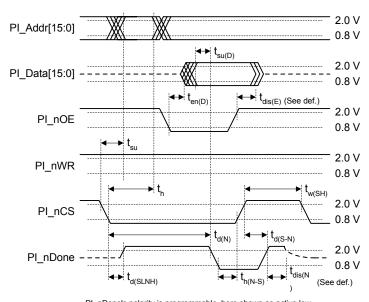

| Figure 30. PI Read Cycle Waveforms                                            | 169         |

| Figure 31. Test Circuit for Signal Disable Test | 170 |

|-------------------------------------------------|-----|

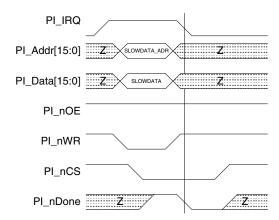

| Figure 32. PI Interrupt Write Cycle             | 171 |

| Figure 33. PI Interrupt Read Cycle              | 171 |

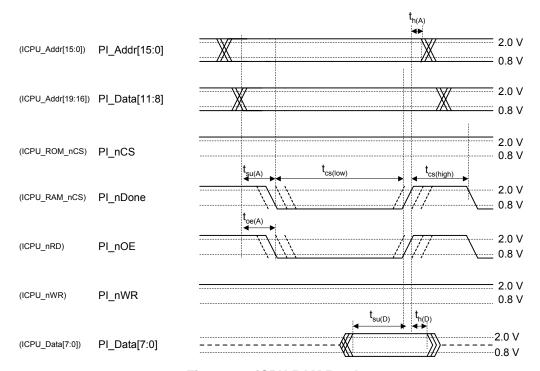

| Figure 34. iCPU RAM Read                        | 172 |

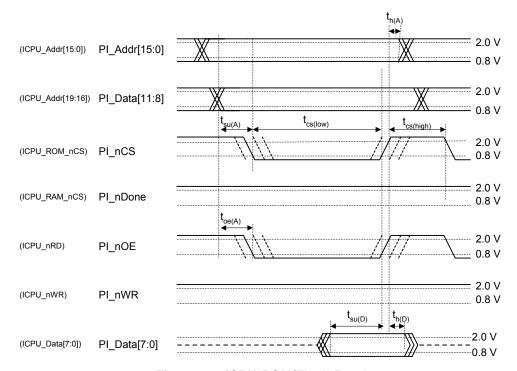

| Figure 35. iCPU ROM/Flash Read                  | 174 |

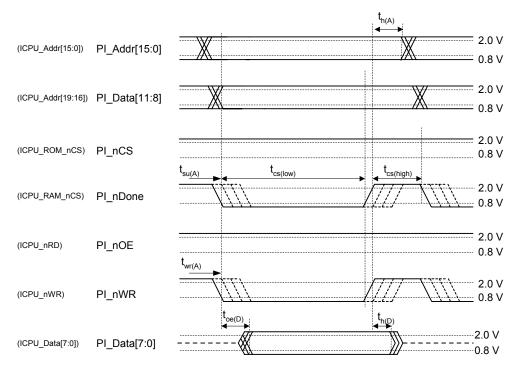

| Figure 36. iCPU RAM Write                       | 176 |

| Figure 37. iCPU Flash Write                     | 178 |

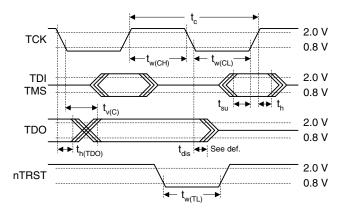

| Figure 38. JTAG Interface Timing Definitions    | 180 |

| Figure 39. Test Circuit for Signal Disable Test | 181 |

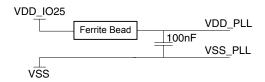

| Figure 40. PLL Supply Filtering                 | 182 |

| Figure 41. PLL Loop Filter Capacitor            | 183 |

| Figure 42. PLL Power and Control Signals        | 183 |

| Figure 43. MDC/MDIO Layout Scheme               | 184 |

| Figure 44. Package Drawing                      | 189 |

# **Tables**

| Table 1. Conditions Triggering a Frame Discard                                                                 | . 27 |

|----------------------------------------------------------------------------------------------------------------|------|

| Table 2. Flow Control Data Receivable After Pause Frame                                                        | . 28 |

| Table 3. Flow Control Thresholds to Avoid Packet Loss                                                          | . 29 |

| Table 4. Frame Priority Parameters                                                                             | . 31 |

| Table 5. Frame Classes                                                                                         | . 33 |

| Table 6. Basic Frame Analysis Data                                                                             | . 34 |

| Table 7. MAC Address Table                                                                                     | . 36 |

| Table 8. MAC Table Layout                                                                                      | . 37 |

| Table 9. Categorizer Classes                                                                                   | . 41 |

| Table 10. Packet Header Format                                                                                 | . 47 |

| Table 11. Pin Name Mapping between iCPU and Parallel Interface                                                 | . 54 |

| Table 12. Control Signal Width as a Function of the CKCON::MD2-0 SFR Value                                     | . 55 |

| Table 13. SFRs Associated with a Particular Interrupt                                                          | . 58 |

| Table 14. Deviation Between Desired and Actual Baud Rate for Selected Clock Frequencies and Desired Baud Rates | . 63 |

| Table 15. Spanning Tree Protocol Port State Properties                                                         | . 68 |

| Table 16. Spanning Tree Protocol Port State Configuration of Stansted                                          | . 69 |

| Table 17. Multiple Spanning Tree Protocol Port State Configuration of Stansted                                 | 69   |

| Table 18. Functional Blocks                                                                                    | . 70 |

| Table 19. SFR Register Overview                                                                                | . 71 |

| Table 20. Block Address Structure                                                                              | . 73 |

| Table 21. Number Of Dummy Bytes and Maximum Serial Interface Clock                                             | . 75 |

| Table 22. SI Configuration Register                                                                            | . 76 |

| Table 23. PI Interface Signals                                                                                 | . 76 |

| Table 24. Register Mapping in PI Address Space                                                                 | . 78 |

| Table 25. PI Bus 8-bit Data Width Example                                                                      | . 79 |

| Table 26. Minimum Register Set to Set Up                                                                       | . 79 |

| Table 27. System Block Registers (Block 7)                                                                     | . 82 |

| Table 28. MAC Block Registers (Block 1)                                                                        | . 82 |

| Table 29. Shared FIFO Block Registers (Block 1)                                                                | . 83 |

| Table 30. Categorizer Block Registers (Block 1)                                                                | . 83 |

| Table 31. Statistics Block Registers (Block 1)                                                                 | . 84 |

| Table 32. Detailed Counters Block Registers (Block 1)                                       | . 84 |

|---------------------------------------------------------------------------------------------|------|

| Table 33. MII Management Bus Block Registers (Block 3)                                      | . 85 |

| Table 34. Memory Initialization Block Registers (Block 3)                                   |      |

| Table 35. Frame Arbiter Block Registers (Block 5)                                           | . 85 |

| Table 36. CPU Capture Block Registers (Block 4)                                             | . 86 |

| Table 37. Frame Analyzer Block Registers (Block 2)                                          | . 86 |

| Table 38. CPU Transfer Mode - CPUMODE (Address 00h)                                         | 87   |

| Table 39. SI Padding - SIPAD (Address 01h)                                                  | . 88 |

| Table 40. PI BusWidth - PIWIDTH (Address 02h)                                               | 88   |

| Table 41. Internal CPU Control - ICPU_CTRL (Address 10h)                                    | 88   |

| Table 42. Internal CPU On-Chip RAM address - ICPU_ADDR (Address 11h)                        | 89   |

| Table 43. Internal CPU On-Chip RAM data - ICPU_DATA (Address 12h)                           | 90   |

| Table 44. Semaphore Register - HWSEM (Address 13h)                                          | 90   |

| Table 45. Global Reset - GLORESET (Address 14h)                                             | 90   |

| Table 46. Mailbox Value - ICPU_MBOX_VAL (Address 15h)                                       | 91   |

| Table 47. Mailbox Set - ICPU_MBOX_SET (Address 16h)                                         | 91   |

| Table 48. Mailbox Clear - ICPU_MBOX_CLR (Address 17h)                                       | 91   |

| Table 49. Chip Identification - CHIPID (Address 18h)                                        | 92   |

| Table 50. External Data Memory Access Control Configuration - CPU_RAM_CFG (Address 19h)     | . 92 |

| Table 51. External Program Memory Access Control Configuration - ICPU_ROM_CFG (Address 1Ah) | . 93 |

| Table 52. Time Compare Value - TIMECMP (Address 24h)                                        | 93   |

| Table 53. SlowData - SLOWDATA (Address 2Ch)                                                 | 93   |

| Table 54. CPU Control - CPUCTRL (Address 30h)                                               | 94   |

| Table 55. General Purpose IO - GPIO (Address 34h)                                           | 94   |

| Table 56. MAC Config - MACCONF (Address 00h)                                                | 95   |

| Table 57. Half Duplex Gaps - MACHDXGAP (Address 02h)                                        | 96   |

| Table 58. Flow Control Setup - FCCONF (Address 04h)                                         | 97   |

| Table 59. Flow Control SMAC High - FCMACHI (Address 08h)                                    | 97   |

| Table 60. Flow Control SMAC Low - FCMACLO (Address 0Ch)                                     | 97   |

| Table 61. Max Length - MAXLEN (Address 10h)                                                 | 97   |

| Table 62. Shaper Setup - SHAPECONF (Address 11h)                                            | 98   |

| Table 63. Policer Setup - POLICECONF (Address 12h)                                          | 98   |

| Table 64. Multicast Storm Setup - MCSTORMCONF (Address 13h)                                 | . 98 |

| Table 65. | Advanced Port Mode Setup - ADVPORTM (Address 19h)        | . 99 |

|-----------|----------------------------------------------------------|------|

| Table 66. | Transmit Modify Setup - TXUPDCFG (Address 24h)           | . 99 |

| Table 67. | CFI Drop Counter - CFIDROP (Address 25h)                 | . 99 |

| Table 68. | CPU Transmit DATA - CPUTXDAT (Address C0h)               | 100  |

| Table 69. | MISC Control Register - MISCFIFO (Address C4h)           | 100  |

| Table 70. | Pool Control Register - POOLCFG (Address CCh)            | 100  |

| Table 71. | Drop Control Register - DROPCFG (Address DCh)            | 101  |

| Table 72. | Misc Status - MISCSTAT (Address C8h)                     | 101  |

| Table 73. | Free RAM Counter - FREEPOOL (Address D8h)                | 102  |

| Table 74. | Categorizer Config - CATCONF (Address 60h)               | 102  |

| Table 75. | Categorizer Map Tag - CATTAG (Address 64h)               | 103  |

| Table 76. | Categorizer SUBMap Tag - CATSUBTAG (Address 65h)         | 103  |

| Table 77. | EtherType Register - CATETHT (Address 68h)               | 104  |

| Table 78. | DSAP Register - CATDSAP (Address 6Ch)                    | 104  |

| Table 79. | IP Protocol Register - CATIPPRT (Address 70h)            | 104  |

| Table 80. | Categorizer Priorities - CATPRIO (Address 74h)           | 104  |

| Table 81. | Categorizer SubPriorities - CATSUBPRIO (Address 75h)     | 105  |

| Table 82. | DS Mapping Register High - CATDSMAPH (Address 78h)       | 105  |

| Table 83. | DS Mapping Register Low - CATDSMAPL (Address 79h)        | 105  |

| Table 84. | DS SubMapping Register High - CATDSSUBMAPH (Address 7Ah) | 106  |

| Table 85. | DS SubMapping Register Low - CATDSSUBMAPL (Address 7Bh)  | 106  |

| Table 86. | PVID Register - CATPVID (Address 7Ch)                    | 106  |

| Table 87. | TCP/UDP Port Register 1 - CATPORT1 (Address 80h)         | 106  |

| Table 88. | TCP/UDP Port Register 2 - CATPORT2 (Address 84h)         | 107  |

| Table 89. | TCP/UDP Port Register 3 - CATPORT3 (Address 88h)         | 107  |

| Table 90. | TCP/UDP Port Register 4 - CATPORT4 (Address 8Ch)         | 107  |

| Table 91. | TCP/UDP Port Register 2 - CATPORT5 (Address 90h)         | 107  |

| Table 92. | Rx Total Bad Packets - RXBADPKT (Address 37h)            | 108  |

| Table 93. | Rx Control Packets - RXCTRL (Address 39h)                | 108  |

| Table 94. | Rx Pause Frames - C_RXPAUSE (Address 3Dh)                | 108  |

| Table 95. | Tx Pause Frames - C_TXPAUSE (Address 3Eh)                | 108  |

| Table 96. | Rx Classified Drops - C_RXCATDROP (Address 3Fh)          | 108  |

| Table 97. | Tx Total Error Packets - TXERR (Address 44h)             | 108  |

| Table 98. | Rx Octets - C_RXOCT (Address 50h)                        | 109  |

| Table 99. Tx Octets - C_TXOCT (Address 51h)               | 109 |

|-----------------------------------------------------------|-----|

| Table 100. Rx Drops - C_RXDROP (Address A0h)              | 109 |

| Table 101. Rx Packets - C_RXPKT (Address A1h)             | 109 |

| Table 102. Rx Broadcasts - C_RXBC (Address A2h)           | 109 |

| Table 103. Rx Multicasts - C_RXMC (Address A3h)           | 110 |

| Table 104. Rx CRC/ALIGN - C_RXCRC (Address A4h)           | 110 |

| Table 105. Rx Undersize - C_RXSHT (Address A5h)           | 110 |

| Table 106. Rx Oversize - C_RXLONG (Address A6h)           | 110 |

| Table 107. Rx Fragments - C_RXFRAG (Address A7h)          | 110 |

| Table 108. Rx Jabbers - C_RXJAB (Address A8h)             | 110 |

| Table 109. Rx 64 Bytes - C_RX64 (Address A9h)             | 111 |

| Table 110. Rx 65-127 Bytes - C_RX65 (Address AAh)         | 111 |

| Table 111. Rx 128-255 Bytes - C_RX128 (Address ABh)       | 111 |

| Table 112. Rx 256-511 Bytes - C_RX256 (Address ACh)       | 111 |

| Table 113. Rx 512-1023 Bytes - C_RX512 (Address ADh)      | 111 |

| Table 114. Rx 1024-long Bytes - C_RX1024 (Address AEh)    | 111 |

| Table 115. Tx Drops - C_TXDROP (Address AFh)              | 112 |

| Table 116. Tx Packets - C_TXPKT (Address B0h)             | 112 |

| Table 117. Tx Broadcasts - C_TXBC (Address B1h)           | 112 |

| Table 118. Tx Multicasts - C_TXMC (Address B2h)           | 112 |

| Table 119. Tx Collisions - C_TXCOL (Address B3h)          | 112 |

| Table 120. Tx 64 Bytes - C_TX64 (Address B4h)             | 112 |

| Table 121. Tx 65-127 Bytes - C_TX65 (Address B5h)         | 113 |

| Table 122. Tx 128-255 Bytes - C_TX128 (Address B6h)       | 113 |

| Table 123. Tx 256-511 Bytes - C_TX256 (Address B7h)       | 113 |

| Table 124. Tx 512-1023 Bytes - C_TX512 (Address B8h)      | 113 |

| Table 125. Tx 1024-long Bytes - C_TX1024 (Address B9h)    | 113 |

| Table 126. Tx FIFO Drops - C_TXOVFL (Address BAh)         | 113 |

| Table 127. Rx High Priority Frames - C_RXHP (Address BBh) | 114 |

| Table 128. Rx Low Priority Frames - C_RXLP (Address BCh)  | 114 |

| Table 129. Tx High Priority Frames - C_TXHP (Address BDh) | 114 |

| Table 130. Tx Low Priority Frames - C_TXLP (Address BEh)  | 114 |

| Table 131. MII-M Status - MIIMSTAT (Address 00h)          | 114 |

| Table 132. MII-M Command - MIIMCMD (Address 01h)          | 115 |

| Table 133. MII-M Return Data - MIIMDATA (Address 02h)            | 115 |

|------------------------------------------------------------------|-----|

| Table 134. MII-M Prescaler - MIIMPRES (Address 03h)              | 115 |

| Table 135. MII-M Scan setup - MIIMSCAN (Address 04h)             | 115 |

| Table 136. MII-M Scan Results - MIIMSRES (Address 05h)           | 116 |

| Table 137. Initialize - MEMINIT (Address 00h)                    | 116 |

| Table 138. Read Result - MEMRES (Address 01h)                    | 116 |

| Table 139. Arbiter Empty - ARBEMPTY (Address 0Ch)                | 117 |

| Table 140. Arbiter Discard - ARBDISC (Address 0Eh)               | 117 |

| Table 141. Read Pointer - CAPREADP (Address 00h)                 | 118 |

| Table 142. Write Pointer - CAPWRP (Address 03h)                  | 118 |

| Table 143. Full Reset - CAPRST (Address FFh)                     | 118 |

| Table 144. Advanced Learning Setup - ADVLEARN (Address 03h)      | 119 |

| Table 145. IP Multicast Flood Mask - IFLODMSK (Address 04h)      | 119 |

| Table 146. VLAN Source Port Mask - VLANMASK (Address 05h)        | 119 |

| Table 147. Mac Address High - MACHDATA (Address 06h)             | 119 |

| Table 148. Mac Address Low - MACLDATA (Address 07h)              | 120 |

| Table 149. Station Move Logger - ANMOVED (Address 08h)           | 120 |

| Table 150. Aging Filter - ANAGEFIL (Address 09h)                 | 120 |

| Table 151. Event Sticky Bits - ANEVENTS (Address 0Ah)            | 120 |

| Table 152. Event Sticky Mask - ANCNTMSK (Address 0Bh)            | 121 |

| Table 153. Event Sticky Counter - ANCNTVAL (Address 0Ch)         | 121 |

| Table 154. Learn Mask - LERNMASK (Address 0Dh)                   | 122 |

| Table 155. Unicast Flood Mask - UFLODMSK (Address 0Eh)           | 122 |

| Table 156. Multicast Flood Mask - MFLODMSK (Address 0Fh)         | 122 |

| Table 157. Receive Mask - RECVMASK (Address 10h)                 | 122 |

| Table 158. Aggregation Mode - AGGRCNTL (Address 20h)             | 122 |

| Table 159. Aggregation Masks - AGGRMSKS (Address 30h - 3Fh)      | 123 |

| Table 160. Destination Port Masks - DSTMASKS (Address 40h - 7Fh) | 123 |

| Table 161. Source Port Masks - SRCMASKS (Address 80h - 8Bh)      | 123 |

| Table 162. Mac Table Command - MACACCES (Address B0h)            | 123 |

| Table 163. Mac Table Index - MACTINDX (Address C0h)              | 124 |

| Table 164. VLAN Table Command - VLANACES (Address D0h)           | 125 |

| Table 165. VLAN Table Index - VLANTINDX (Address E0h)            | 125 |

| Table 166. Analyzer Config Register - AGENCNTL (Address F0h)     | 125 |

| Table 167. General Purpose I/O Input - GPIO_IN (Address 80h)                          | 126 |

|---------------------------------------------------------------------------------------|-----|

| Table 168. General Purpose I/O Output - GPIO_OUT (Address 90h)                        | 126 |

| Table 169. General Purpose I/O Output Enable - GPIO_OE (Address A0h)                  |     |

| Table 170. General Purpose I/O Status - GPIO_STAT (Address A1h)                       | 127 |

| Table 171. Data Pointer 1 Low - DPL1 (Address 84h)                                    | 127 |

| Table 172. Data Pointer 1 High - DPH1 (Address 85h)                                   | 128 |

| Table 173. Data Pointer Select - DPS (Address 86h)                                    | 128 |

| Table 174. Special Function Register - SPC_FNC (Address 8Fh)                          | 129 |

| Table 175. Paging Control - PAGE (Address B0h)                                        | 129 |

| Table 176. Watchdog Data - WDDA (Address A2h)                                         | 130 |

| Table 177. Watchdog Control - WDCON (Address A3h)                                     | 130 |

| Table 178. Timer Clock and External Memory Stretch Cycles Control CKKON (Address 8Eh) | 131 |

| Table 179. Interrupt Enable - IE (Address A8h)                                        | 132 |

| Table 180. Interrupt Priority - IP (Address B8h)                                      | 132 |

| Table 181. Timer 2 Control - T2CON (Address C8h)                                      | 133 |

| Table 182. Timer 2 Capture Low - RCAP2L (Address CAh)                                 | 133 |

| Table 183. Timer 2 Capture High - RCAP2H (Address CBh)                                | 133 |

| Table 184. Timer 2 Low - TL2 (Address CCh)                                            | 134 |

| Table 185. Timer 2 High - TH2 (Address CDh)                                           | 134 |

| Table 186. Register Access Done - RA_DONE (Address F8h)                               | 135 |

| Table 187. Register Access Block and Subblock - RA_BLK (Address F9h)                  | 135 |

| Table 188. Register Access Read Address - RA_AD_RD (Address FAh)                      | 135 |

| Table 189. Register Access Write Address - RA_AD_WR (Address FBh)                     | 135 |

| Table 190. Register Access Data Byte #0 - RA_DA0 (Address FCh)                        | 136 |

| Table 191. Register Access Data Byte #1 - RA_DA1 (Address FDh)                        | 136 |

| Table 192. Register Access Data Byte #2 - RA_DA2 (Address FEh)                        | 136 |

| Table 193. Register Access Data Byte #3 - RA_DA3 (Address FFh)                        | 136 |

| Table 194. Program Status Word - PSW (Address D0h)                                    | 137 |

| Table 195. Pin Type Definitions                                                       | 138 |

| Table 196. Clk Interface                                                              | 139 |

| Table 197. RGMII Ports                                                                | 139 |

| Table 198. Power and Ground                                                           | 140 |

| Table 199. JTAG Interface                                                             | 140 |

| Table 200. iCPU External Memory Interface                                             | 141 |

| Table 201. | iCPU GPIO and RS232 Interface                                       | 142 |

|------------|---------------------------------------------------------------------|-----|

| Table 202. | iCPU Pin Mapping to the PI Interface                                | 142 |

| Table 203. | PI Interface                                                        | 144 |

| Table 204. | SI Interface                                                        | 145 |

| Table 205. | MII Management Interface                                            | 145 |

| Table 206. | GPIO Signals                                                        | 145 |

| Table 207. | Miscellaneous Signals                                               | 146 |

| Table 208. | Signal List by Ball Number                                          | 147 |

| Table 209. | Signal List by Signal Name                                          | 152 |

| Table 210. | Recommended Operating Conditions                                    | 157 |

| Table 211. | Absolute Maximum Ratings                                            | 157 |

| Table 212. | DC Specifications for Clock                                         | 158 |

| Table 213. | DC Specifications for RGMII and MII Management                      | 159 |

| Table 214. | DC Specifications for PI, iCPU, SI, JTAG, and Other Control Signals | 159 |

| Table 215. | Maximum Operating Current                                           | 160 |

| Table 216. | Typical Current Consumption                                         | 161 |

| Table 217. | Power Dissipation                                                   | 161 |

| Table 218. | System Clock AC Specifications                                      | 162 |

| Table 219. | nReset AC Specifications                                            | 163 |

| Table 220. | RGMII 1000 Mbps AC Specifications                                   | 164 |

| Table 221. | RGMII 10/100 Mbps AC Specifications                                 | 164 |

| Table 222. | MII Management AC Specifications                                    | 166 |

| Table 223. | SI Interface AC Specifications                                      | 167 |

| Table 224. | PI Interface AC Specifications                                      | 170 |

| Table 225. | iCPU RAM Read Specifications                                        | 173 |

| Table 226. | iCPU ROM/Flash Read Specifications                                  | 175 |

| Table 227. | iCPU RAM Write Specifications                                       | 177 |

| Table 228. | iCPU Flash Write Specifications                                     | 179 |

| Table 229. | JTAG AC Specifications                                              | 180 |

| Table 230. | Flash Access Timing                                                 | 187 |

| Table 231. | Thermal Resistances                                                 | 190 |

### **Functional Overview**

The VSC7384 Stansted device can operate as either a VLAN aware switch or a VLAN unaware switch. It forwards frames at Layer 2 based on information up to and including Layer 4.

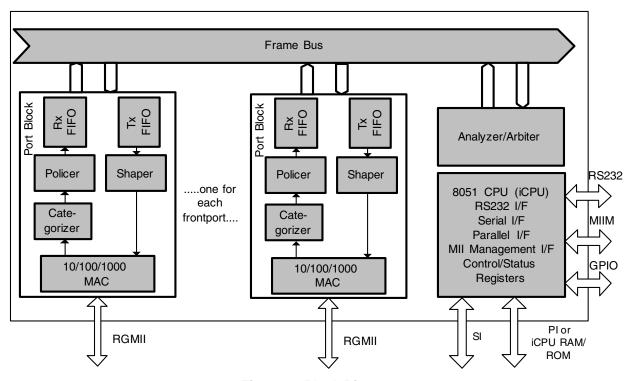

Figure 1. Block Diagram

## **Tri-Speed Gigabit MACs**

The Stansted device implements 12 separate tri-speed Ethernet MACs designed to comply with IEEE 802.3-2002. The tri-speed MACs support full duplex operation at 10/100/1000 Mbps and half duplex operation at 10/100 Mbps.

## **Register Access**

The control block receives commands from either the iCPU or from an off-chip controller/processor. The commands can be divided into four categories:

- MII Management reads and writes for PHY control

- · Configuration

- · Status or statistics gathering

- Capture and transmission of packets

## **Link Aggregation**

Stansted supports ingress and egress port aggregation. Any number of ports can be aggregated into any number of groups with a frame distribution function based on the Source MAC address, the Destination MAC address, or a combination of both.

### **VLAN Support**

Stansted can be configured as either VLAN unaware (behaving transparently against VLAN tagged frames) or as VLAN aware.

When VLAN is enabled, frames received without a VLAN tag on a given port are tagged with a port specific, configurable VLAN number. Frames that already have a VLAN tag when they are received have no additional tag added.

VLAN awareness (and thus tagging/untagging of frames) can be configured on a per-port basis, which is a very powerful feature for advanced applications.

Stansted can set up and maintain 4096 VLANs.

Furthermore, each port can be configured to a set of ports it can forward to, thereby facilitating port-based VLANs. By default, all ports can forward to all others.

### 802.1 Q-in-Q Support

Q-in-Q is an efficient method for enabling Subscriber Aggregation. This is very useful in, but is not limited to, Metropolitan Area Network (MAN) applications. Q-in-Q is, in effect, the use of double VLAN tags.

In Stansted, Q-in-Q is supported in three ways:

- 1. Each port can add or strip a VLAN tag (independently configurable for ingress and egress per port).

- 2. Frame priority can be determined based on information in the outer VLAN tag.

- 3. The frame can be forwarded based on information in the outer VLAN tag.

If several Stansteds are used to aggregate a number of subscribers towards the edge of the network, the Q-in-Q support can be used to store prioritization information and the source port number of each frame for use by subsequent Stansteds. In this application, prioritization need only be done once, because the network edge router easily stores the route back to the subscriber from where the frame originated.

The effective maximum frames size will be 1526 bytes throughout the Q-in-Q network, as the standard end-station MTU of 1518 bytes gets appended with two VLAN tags.

### **Quality of Service**

The Stansted device supports four priority levels. On each port, an enhanced classifier/categorizer assigns priorities based on information taken from Layer 2 to Layer 4.

The Categorizer analyzes all received frames. It assigns each frame to one of four priority levels based on:

- 1. Priority in the IEEE802.1Q (VLAN) tag

- 2. Differentiated Services Code Point (DSCP) from the IP-header

- 3. TCP/UDP port

- 4. DSAP Value

- 5. EtherType field

- 6. Priority in a Q-in-Q tag

Based on the priority determined by the Categorizer, higher priority traffic takes precedence over lower priority traffic during forwarding through the switching engine. When congestion occurs, the traffic with the lowest priority is dropped before traffic with higher priority. Latency is minimized for expedited data because the two highest priority levels can overtake the two lowest priority levels.

#### Flow Control

All ports can be independently configured to use nondropping flow control and to enable the use of Asymmetric Flow Control. The programmer can set up individual high and low thresholds for each FIFO. These thresholds control the start and stop of pause signaling. The internal FIFOs have enough memory to handle flow control on short-haul, full duplex lines without using excessive pause signaling.

The switch generates flow control when necessary to ensure frames are never dropped, or it can be programmed to discard low priority traffic first in case of congestion.

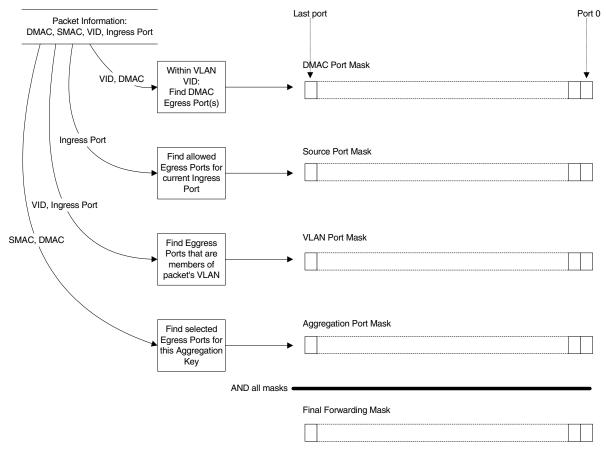

## **Packet Forwarding Analysis**

The advanced filtering and forwarding capabilities of the Stansted device are a result of the work carried out by the Analyzer.

The Analyzer maintains and uses three tables for packet forwarding: a source port table, a VLAN table, and a destination address table. When frame header information is extracted from an incoming packet, the Analyzer uses these tables to look up the following information:

- A 12-bit Source Port Mask (one bit per port)

- A 12-bit VLAN Mask

- A 12-bit Destination Port Mask (if the DMAC address is known, otherwise a programmable mask)

These three masks are combined by a bit-by-bit AND operation, and the results are adjusted to reflect any active link aggregations. The resulting bit mask is forwarded to the Arbiter as the next forwarding decision for the given source port.

By default, the three masks are set up so that:

- Packets received on a given port cannot be forwarded to that same port.

- There is no VLAN present (all ports are members of all VLANs, frame tags are not examined).

- Packets to a given destination address are forwarded only to the port where the destination was learned.

### **MAC Address Learning**

When a packet is received, the source MAC address is looked up in the destination address table (see "Packet Forwarding Analysis" on page 21). If it is not presently registered and it is not a multicast address, a new entry is created. If necessary, an entry is discarded to make room for the new one based on a "least recently used" algorithm.

The Stansted device is capable of looking up or adding all incoming entries to the MAC table at maximum load. This process is referred to as "wire-speed learning".

Addresses can also be locked using a CPU external to Stansted or the iCPU by writing into the table. Locked entries are never discarded.

# **Shaping and Policing**

The Stansted device provides per-port policing as well as per-port shaping. Policing can be used to limit incoming subscriber streams according to a traffic contract, and shaping can be used to protect a receiving device against high bandwidth bursts.

Based on a leaky bucket algorithm, the Shaper as well as the Policer support a bit rate granularity of 244 kbps for 1 G, 48.8 kbps for 100 M, and 4.88 kbps for 10 M. Spanning Tree and IGMP control frames are only forwarded to the CPU capture facility and will not be policed from the stream.

The ingress Policer can initiate flow control messages, enabling dropless policing.

An additional leaky-bucket system handles the Stansted's Broadcast and Multicast Storm Control.

#### **CPU Interfaces**

The Stansted device provides three interfaces to core registers of which two are mutually exclusive. The three interfaces are:

- An 8- or 16-bit Parallel Interface (PI)

- On-chip 8051 CPU Interface

- A serial, SPI-style, 4-wire interface (SI)

The serial interface exists in all configurations of the Stansted. It allows interfacing to a vast amount of microcontrollers and is capable of transferring approximately 2.5 MBps.

The Parallel Interface and the on-chip 8051 CPU (iCPU) Interface are mutually exclusive as they use the same external interface. The selection between the two is made with a strapping pin named ICPU\_PI\_En. Strapping the pin low enables the Parallel Interface, whereas strapping the pin high enables the iCPU.

With the ICPU\_PI\_En pin strapped low, the Stansted operates as a slave on an external CPU parallel bus. The PI connects to many well-known processors, like the PowerPC® and ARM® CPUs when operated in 16-bit mode. In addition, the PI interface can be configured to run in 8-bit mode, allowing it to work with an 8-bit CPU system such as an external 8051 controller. The PI can handle about 25 MBps.

With the ICPU\_PI\_En pin strapped high, the iCPU is enabled, and the aforementioned parallel interface is used as a RAM/Flash interface for programs running within the iCPU. The iCPU is a standard 8-bit 8051 microcontroller with a number of add-on modules extending the basic 8051 functionality. It is designed to replace an external CPU by providing monitoring and configuration functions and the transmission of packets for STP and GxRP (GARP, GVRP, and so forth) protocols, in addition to direct access to the output queues.

Besides standard 8051 functionality, the iCPU features 8 kilobytes of on-chip RAM accessible as both program and data memory and 256 bytes of scratchpad RAM (internal RAM). Both RAMs can be accessed from an external CPU connected to the SI interface, enabling external debugging.

The glueless connection to most commercial Flashes and RAMs is made through the shared 16-bit address and 8-bit data buses with the option of extending the address bus with four bits through a paging mechanism, allowing for up to 1 Mbyte of external data RAM and up to 1 megabyte (Mb) of external program memory (Flash or ROM). The external interface's read and write timing can be configured separately for read and write accesses and for code and data accesses.

The iCPU uses only 4 clock cycles per instruction compared to the original 8051 CPU, which uses 12 clock cycles. In addition, the clock frequency can be changed dynamically (7.8125 to 62.5 MHz) to meet the timing of external memories and speed up execution if running in internal memories only.

The iCPU has access to a standard RS232 interface, three timers, a watchdog, and four additional GPIO pins, one of which may be used for externally controlled program single-stepping.

Software synchronization and handshaking between the iCPU and a possible external CPU connected to the device's SI interface is made possible through a mailbox accessible by both CPUs.

The iCPU supports industry-standard compilers and assemblers.

### **MII Management Interface**

Set up and status monitoring of connected PHYs is done through the built-in MII Management controller. It is capable of connecting to up to 32 PHYs.

The controllers are suitable for direct connection to standard RGMII PHYs and are accessed using the CPU interfaces.

# **General Purpose I/Os**

The Stansted features five general purpose I/Os (GPIO). These pins are freely configurable as either inputs or outputs and are accessed through either CPU interface.

# **Functional Description**

This section provides detailed information on aspects of the Stansted device's functionality that were highlighted in the features list and general description sections of this document. It should be noted, however, that many device features and settings not mentioned here. To learn more about any of these functions and settings, refer to the Configuration and Register Description descriptions of this document.

#### Introduction – A Packet's Life in the Stansted Device

In this section, several functional blocks of the Stansted that are referenced in Figure 1, the "Block Diagram", in Functional Overview section, are explained using a discussion of the "life" of a packet in the device, which is shown in Figure 2.

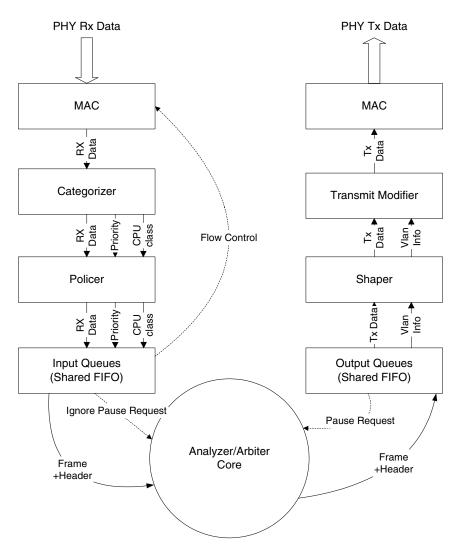

Figure 2. The Life of a Packet

### **Switch Engine Operation and Congestion Control**

Each Stansted port is equipped with a MAC that receives and validates data from the PHY. From the Mac, the data is passed through the Categorizer for frame priority determination, the Policer for subscriber control. The data is then sent into one of the port ingress queues.

The packets are dequeued and forwarded on the internal frame bus as soon as it becomes available. The port or ports the packet is destined for receive the packet into one of the egress queues. As soon as the MAC is ready for transmission, the packet is dequeued and transmitted through the Shaper for subscriber control. The packet then goes through the modifier where a VLAN tag is added to the frame (if VLAN tagging is configured), and finally sent to the PHY.

Each port has a 16 kilobyte (kB) pool of memory that is shared between the ingress and egress queues for storing frames.

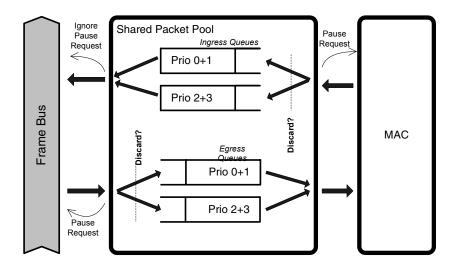

Figure 3. Shared Packet Pool

The priority determined by the Categorizer is used to select the ingress or egress queue during the enqueuing process. The priority ranges from 0 (lowest) to 3 (highest), and the traffic from different priority levels is, to some degree, split into different queues upon receipt. During dequeuing, the 2+3 queues are checked before the 0+1 queue. This causes the packets with higher priorities to overtake the packets with lower priorities.

Each port of Stansted can be programmed to handle congestion, either by discarding frames when specific fill levels are reached, or by requesting flow control from the sources of additional packets. The required type of congestion control for a switch application that uses the Stansted device is network dependant.

In the shared pool, the memory allocation unit is 256 bytes, and each port has its own 64 units of memory, resulting in a total of 16 kB of memory per port. For protection against overflow in the pool, the SharedFIFO register group contains various registers that can be used to select pause requests and discard conditions.

#### **Priority Based Frame Discard**

When a frame is added to a queue, the current amount of pending packet data is checked against a threshold. If adding the frame causes the queue to go over the threshold, the frame is discarded. The threshold is determined by the priority of the incoming frame. This allows a portion of the memory to be reserved for higher priority traffic.

The DROPCFG and MISCFIFO registers contain the thresholds, used as described in Table 1.

Table 1. Conditions Triggering a Frame Discard

| Frame Priority | Discarded if Condition is Above |  |

|----------------|---------------------------------|--|

| 0              | DROPCFG.LOW - MISCFIFO.SUBDIST  |  |

| 1              | DROPCFG.LOW                     |  |

| 2              | DROPCFG.HIGH - MISCFIFO.SUBDIST |  |

| 3              | DROPCFG.HIGH                    |  |

In the DROPCFG register, there are two thresholds, HIGH and LOW, for both the ingress and the egress. The thresholds are determined based on the total amount of ingress and egress data. For example, if DROPCFG.LOW=10, DROPCFG.HIGH=20, and MISCCONF.SUBDIST=4, ingress frames with a priority of 2 are dropped if more than 16 slices of ingress data are used; frames with a priority of 1 are dropped if more than 10 are used.

#### **Pausing Streams using Flow Control**

Another method of avoiding memory overflow is to request flow control from the data source. This is typically accomplished by asking the MAC to pause the link partner, which it does in cases of ingress overflow by issuing MAC pause frames (or throttle back collisions, when the device is configured for half duplex operation). In cases of egress overflow, flow control is accomplished by telling the Arbiter (see Figure 2) that no more room is available for egress packets.

There is a set of thresholds for each direction. They are located in the POOLCFG register. The set is used for hysteresis purposes. For example, if POOLCFG..INGRESSLOW=10, and POOLCFG.INGRESSHIGH=20 the MAC is asked to pause incoming frames when more than 20 slices of ingress data are used, and to cancel this request when less than 10 are left.

#### **Advanced Drop Mode**

When running the port in Drop mode, the possibility of overflow is avoided because frames are dropped depending upon their priority. When in Drop mode, the general performance of the device can be improved by using a limited version of flow control. This is done by enabling the internal flow control from egress back to ingress to some degree. This keeps the data in the ingress queues to avoid egress overflow. This has head-of-line blocking effects, which can be solved by enabling forward pressure on the ports (Ignore Pause in Figure 3). The effects for the two frame directions are discussed later in this document.

#### **Egress**

When the amount of egress data exceeds POOLCFG.EGRESSHIGH, the ingress ports are stopped from forwarding more data. In this case, the congestion is fed back to the ingress queues.

#### Ingress

If an egress port has blocked further transfers, the forwarding stops until the POOLCFG.INGRESSHIGH threshold is reached.

The forwarding pressure option is enabled through the POOLCFG register (Ingress Protection Method). It is enabled by default.

#### **Flow Control Mode**

When running a port in the flow control mode, no packet drop is allowed on the port, and memory depletion must be handled by flow controlling the source of additional data. In this mode, the DROPCFG register must be set to not drop any packets at all. This is accomplished by setting all thresholds to 63 because the theoretical maximum consumption from either ingress or egress is 61 memory units. The flow control mechanism is handled through the POOLCFG register.

Asymmetric flow control, where only ingress or egress has flow control enabled, is supported by enabling flow control in the desired direction only. Egress flow control is enabled through the "Obey Flow Control" option in the FCCONF register, and ingress flow control can be enabled through the "Ingress Protection Method" option in the POOLCFG register.

#### Flow Control Thresholds

Thresholds must be set with care to avoid packet loss in all cases (provided that no pause frames are lost). The amount of data that can be received from the moment the MAC is asked to send a pause frame until the last byte from the remote partner has been received is defined here:

2 x (maximum frame size) + [media occupied] 2 x (cable length) x 5 bits x (speed / 1000) + [data on cable] 250 bytes [various reaction times]

This value varies for different speeds and cable lengths, as shown in Table 2. Standard Ethernet frame sizes are assumed with sizes up to 1526 bytes (see "Jumbo Frames," which begins on page 41).

Table 2. Flow Control Data Receivable After Pause Frame

|       | Length        |               |               |               |

|-------|---------------|---------------|---------------|---------------|

| Speed | 10 m          | 100 m         | 550 m         | 2000 m        |

| 10    | 3.1 kilobytes | 3.1 kilobytes |               |               |

| 100   | 3.1 kilobytes | 3.1 kilobytes |               |               |

| 1000  | 3.1 kilobytes | 3.2 kilobytes | 3.8 kilobytes | 5.8 kilobytes |

When setting the thresholds, it is beneficial to have as large a part of the pool memory as possible allocated for egress data. This can be accomplished by setting the thresholds using the values in Table 2 in place of the "X" in Table 3.

Table 3. Flow Control Thresholds to Avoid Packet Loss

| Threshold                                                     | Value                                              |  |

|---------------------------------------------------------------|----------------------------------------------------|--|

| Ingress High                                                  | 4 kilobytes (at least two max size frames)         |  |

| Ingress Low                                                   | 3.5 kilobytes (a small hysteresis)                 |  |

| Egress High 15 kilobytes minus (Ingress High + X from Table 2 |                                                    |  |

| Egress Low                                                    | 15 kilobytes minus (Ingress High + X from Table 2) |  |

The ingress thresholds can be set to other values than the ones suggested. The 15 kilobytes offset used for calculating the egress thresholds is derived from the 16 kilobytes available memory minus the maximum overhead for each queue.

As an example, the configuration for a 1G port on a 550 m media results in thresholds:

- Ingress High=4 kilobytes ~ register value=0x10 (256 bytes slices)

- Ingress Low=3.5 kilobytes ~ register value=0x0e

- Egress High=15 kilobytes (4 kilobytes + 3.8 kilobytes)=7.2 kilobytes ~ register value=0x1d

- Egress Low=Egress High ~ register value=0x1d

#### **MAC Features**

Each of the 12 ports are equipped with a MAC that can operate in various modes. The modes are normally set up in the MACCONF register, where speed, duplex mode, and other options are selected. When changing modes, the port must be reset. This is done by writing the configuration word twice: first with the reset bits set, and then with the reset bits cleared. See Table 38, "CPU Transfer Mode - CPUMODE (Address 00h)", on page 87 for a detailed description on how to reset a port.

The more advanced features of the MAC are configured in the ADVPORTM register where the transmit clock can be inverted and halted. Half duplex settings such as the Frame Gap values are configured in the MACHDXGAP register.

The MAC supports frame lengths up to 12.2 kB. The maximum length accepted by the MAC is configurable in the MAXLEN register.

#### **VLAN Features**

The method used by each port to handle frame tagging and untagging is configured by the Port Controller as described here:

For ingress (Rx) frames, the processing of tagged and untagged frames can be configured as follows:

- For determining the priority of ingress frames:

- If TAG prioritization is in use, the priority field in a tagged frame is used for internal prioritization.

- If TAG prioritization is in use, all untagged frames get a configurable internal priority.

- If TAG prioritization is not in use, the internal prioritization is based on the contents following the tag.

- For determining the VLAN membership:

- The tag can be ignored and the VLAN membership is based solely on the priority determined by the payload. This is used when using Stansted as a VLAN-unaware switch.

- The tag can be used for VLAN membership allocation. Priority tagged frames (VID=0) in this respect are not handled as VLAN tagged, and are treated as an untagged frame.

- Untagged frames are allocated to a VLAN determined by the internal prioritization.

Egress (Tx) frame handling can be configured as follows:

- Do not tag frames. This is used when using the Stansted device as a VLAN-unaware switch or when the port is configured with respect to the VLAN as an ACCESS port.

- Tag all frames. This is used when the port is configured as a trunk port with respect to the VLAN.

- Tag all frames except those with a specific VID. This is used when the port is configured as a hybrid port with respect to the VLAN.

These parameters are configured for each individual port in the CATCONF, CATPVID, and TXUPDCFG registers.

## **Frame Categorization**

Each port has a Frame Categorizer that determines the priority of ingress frames. This priority is in the range 0 to 3, and its use is described in the switching engine section. It is determined by information from layers 2, 3, and 4 within the frame. Several registers in the Categorizer Block Registers are used for configuring this.

#### **Frame Priority Determination**

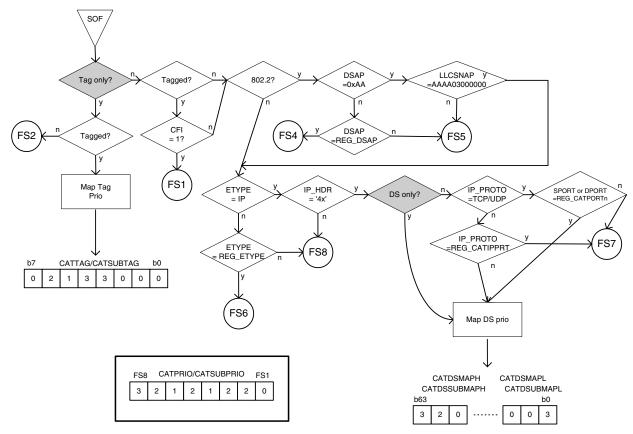

Frame priority determination is based on a set of parameters that can be configured in each port. The parameters are mainly targeted at recognizing specific IP frame types, but other specific frames specified by Layer 2 header fields can be recognized also. The set of configurable parameters are listed in Table 4 and are shown in order of execution in Figure 4 (register values shown in the flow chart are not necessarily default values). Each FSx value in the table is actually a value set in the CATPRIO/CATSUBPRIO registers, which can be programmed from 00 (lowest priority) to 11 (highest priority). The priorities are programmed into the categorizer register as most significant bit in CATPRIO and least significant bit in CATSUBPRIO. As an example: FS1 is set to 1 by setting the FS1 field in CATPRIO to 0 and FS1 field in CATSUBPRIO to 1.

When classifying IP frames, only frames of type IPv4 are recognized as of IP type (IP header version field equals 4). A frame is recognized as an 802.2 frame if the Type/Length field is less than 0x600.

**Table 4. Frame Priority Parameters**

| Parameter | Description                                                                                                                                        |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tag Only  | Priority is always taken from the IEEE802.1D TCI field. Untagged frames are given the priority FS2.                                                |  |

|           | If this option is NOT set, tag information is disregarded, except if CFI in the frame is set. In this case, the priority will be set to FS1.       |  |

| CATDSAP   | IEEE802.2 frames with SNAP encapsulated data will be classified as what is found in the encapsulated data.                                         |  |

|           | IEEE802.2 frames with DSAP matching this register, will get priority FS4.                                                                          |  |

|           | All other IEEE802.2 frames will get priority FS5.                                                                                                  |  |

| CATETHT   | Frames with matching Ethernet type (except IP frames) get priority FS6.                                                                            |  |

|           | IP packets are categorized based on the parameters below.                                                                                          |  |

|           | All other frame types are assigned priority FS8.                                                                                                   |  |

| CATPORTX  | For TCP/UDP Frames: If their source or destination ports match one of these parameters, their priority is based on the IP DS field found in frame. |  |

|           | Nonmatching port numbers result in priority FS7.                                                                                                   |  |

| CATIPPRT  | IP frames (non TCP/UDP) with matching protocol number get their priority based on the IP DS field found in the frame.                              |  |

|           | All other IP frames get priority FS7.                                                                                                              |  |

Figure 4. Categorizer Priority Assignment Flow Chart

#### Example:

All frames with Ethernet type 09A1h are assigned priority 2 and all other frames are assigned priority 0. To do this, set CATETHT=9A1h, CATPRIO.FS6=1, CATSUBPRIO.FS6=0, and all other FSs=0.

When the Tag priority is used, the CATTAG register is used to translate the 8 tag priority values into internal priority. When IP packets' DS fields are used for priority calculation (according to Table 4), the CATDSMAPL/CATDSMAPH + subregisters are used. DS are used either when an IP port or protocol match is found, or when the DS-only flag is set in the CATCONF register. Refer to the register list for further information.

#### **Frame Class Determination**

Another task for the Categorizer is to determine a class for each packet. This class is used in the frame analysis process to decide where to send the packet. The classes recognized by the Categorizer and the codes given to the Analyzer are shown in Table 5.

Table 5. Frame Classes

| Frame Type                             | Condition                                                                                                                  | Class To Analyzer                                                   |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Reserved Addresses (IEEE802.1D 7.12.6) | DMAC=0180C200000x<br>(BPDUs and various Slow Protocols supporting Spanning<br>Tree, Link aggregation, Port Authentication) | FORCECPUONLY<br>(MAC control frames will be<br>filtered by the MAC) |

| IP/ARP MAC broadcast                   | DMAC=BC, Type=IP/ARP                                                                                                       | FORCECPU                                                            |

| IGMP                                   | DMAC=01005Exxxxxxx, Type=IP, IP type IGMP                                                                                  | FORCECPUONLY                                                        |

| IP Multicast Data                      | DMAC=01005Exxxxxxx, Type=IP, non-IGMP, DIP outside 224.0.0.x                                                               | IPMCFLOOD                                                           |

| IP Multicast Ctrl                      | DMAC=01005Exxxxxxx, Type=IP, non-IGMP, DIP inside 224.0.0.x                                                                | FORCECPU                                                            |

| Others                                 | Others                                                                                                                     | NORMAL                                                              |

For a class to be recognized, it must be enabled in the CATCONF register. The class is transferred to the Analyzer module, which uses it in the process of determining the set of egress ports to which each packet should be forwarded. Refer to Table 9.

# **Policing**

The policing feature provides per-port data rate control at a fine granularity and operates on all frame types. There is also a separate Policer dedicated to broadcast and multicast traffic; this enables Broadcast Storm Control.

#### **General Policer**

The POLICECONF register is used to set up the Policer:

- Bit 24:16: "Bucket Threshold": The bucket threshold, measured in units of 512 bytes

- Bit 11:0: "Data Rate": The bucket is emptied with this rate. Rate unit is speed dependent:

- 1G: 244 kbps

- 100M: 48.8 kbps

- 10M: 4.88 kbps

Each incoming packet causes the bucket level to be increased by a number equal to the packet size (without preamble and IFG) measured in bytes. The bucket level is decreased at a steady rate corresponding to the value of the Data Rate bit field.

If the bucket level reaches the Policer threshold, flow control frames are generated. Packets are not discarded. Over time, the bucket level will drop below the threshold. Then, the flow control condition is cleared again.

#### **Broadcast/Multicast Policer**

The Policer used for Broadcast and Multicast Storm Control is set up with the MCSTORMCONF register. Rate parameters are set up like the general Policer.

### **Shaping**

Shaping allows you to manage the data rate for each port in great detail. To set up the shaper, use the SHAPECONF register as described here:

- Bit 24:16: "Bucket Threshold": The bucket threshold, measured in units of 512 bytes

- Bit 11:0: "Data Rate": The bucket is emptied with this rate. Rate unit depends on speed dependent as follows:

- 1 G:244 kbps

- 100 M:48.8 kbps

- 10 M:4.88 kbps

Each packet leaving the switch causes the bucket level to be increased by a number equal to the packet size (without preamble and IFG) measured in bytes. The bucket level is decreased at a steady rate corresponding to the value of the Data Rate bit field.

If the bucket level reaches the Shaper threshold, packets are kept in the egress queue. As no packets are leaving the transmit queues, the bucket level is not increased. Over time, the bucket level will drop below the threshold. Then, packets will be allowed to leave the switch again.

# **Frame Analysis**

### **Tables in the Analyzer**

The central Analyzer module maintains a number of tables and masks. Table 6 lists the most important ones. Refer to the register list for more details.

Table 6. Basic Frame Analysis Data

| Table/Register          | Description                                                                                                                                                          |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAC Table               | 8192 stations learned by CPU or autolearned; each entry in the table is a MAC record                                                                                 |  |

| VLAN Table              | 4096 masks with allowed egress ports for each VID, and a flag – SourceChk - for checking the ingress port as being a member of the VLAN in which frames are received |  |

| Source Port Masks       | 12 port masks with allowed egress ports for each ingress port                                                                                                        |  |

| Destination Port Masks  | 64 port masks with translation of logical port indexes to port masks                                                                                                 |  |

| Aggregation Port Masks  | 16 port masks with allowed egress ports for each Aggregation Key                                                                                                     |  |

| Unicast Flooding Mask   | A port mask indicating where to send unicast packets with unknown destination addresses                                                                              |  |

| Multicast Flooding Mask | A port mask indicating where to send multicast packets with unknown destination addresses; this mask also covers the broadcast address                               |  |

#### **Analysis Overview**

The end result of a frame analysis is the Forwarding Mask. It contains the set of egress ports to which the analyzed frame are forwarded.

The decision to forward is made depending on header information from the incoming packets, user configured tables, autolearned information, and the CPU class reported by the Categorizer (see "Frame Class Determination," which begins on page 33).

The general flow of Frame Analysis is shown in Figure 5. Special cases (analysis exceptions) are not shown, but are described in "Exception Flags," which begins on page 40.

Figure 5. Frame Analysis

The Final Forwarding Mask is a set of egress ports, each of which receives a copy of the packet. This normally includes the ports that pass the four subanalysis steps shown in Figure 5.

#### The MAC Table

Stansted keeps a track of ports by their Destination MAC address by writing to and reading from an internal MAC address table. This table is used in the DMAC Analysis Block where it is checked if the DMAC address in the packet has been previously used as an SMAC address.

The MAC table consists of 8192 records with the contents described in Table 7.

Table 7. MAC Address Table

| MAC Record Field  | Description                                                                 |  |

|-------------------|-----------------------------------------------------------------------------|--|

| MAC Address       | The 48-bit Mac address (matched at lookup)                                  |  |

| VLAN ID           | he 12-bit VLAN ID (matched at lookup)                                       |  |

| Destination Index | Destination Mask number                                                     |  |

| Aged Flag         | Flag: aging has run since last learn of this address                        |  |

| Locked Flag       | Flag: entry is locked. It will not be aged out nor overwritten              |  |

| Valid             | Flag: entry is valid                                                        |  |

| CPUCopy           | Exception Flag: copy frames destined for this DMAC to the CPU buffer        |  |

| FwdKill           | Exception Flag: do not forward packets with this DMAC to any ports          |  |

| Ignore            | VLAN Exception Flag: do not apply VLAN port mask for packets with this DMAC |  |

The table is automatically updated by an autolearning process, a CPU based learning process, or by direct manipulation from the CPU through register accesses (see "Direct MAC Table Access," which begins on page 36). The MAC address and VLAN ID are the identification of the station, the three flags hold the status of the entry, and the three exception flags are for special purposes, as explained later.

For autolearned ports, the Destination Index number is the port number it was learned from. It is used as a pointer into a table of 64 Destination Port Masks, each translating this logical index number into a set of egress ports. In standard setups, only the first 12 Destination Port Masks are used, and by default they are all configured to have only the port bit corresponding to their index set. So, if a station is learned on port 4, its record will have '4' in the destination index, and when packets are sent to the station, Destination Port Mask number 4 will be used—which is a port mask with only the port 4 bit set.

#### **Direct MAC Table Access**

As mentioned, apart from the more automated learning processes, it is also possible to directly access the table in order to dump the contents or to write specific data at specific locations. This is accomplished using the register interface.

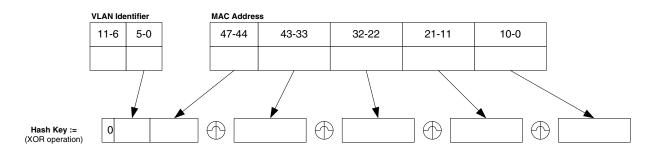

The MAC table is organized as a 2048 x 4 entry hash table. When directly accessing the table, the MACTINDX is first written with the desired record table position, and a Read Entry or Write Entry command is then issued through the MACACCES register. Each operation autoincrements the index to ease dumping or updating the whole table.

| Hash Key | 0          | 1          | 2          | 3          |

|----------|------------|------------|------------|------------|

| 0        | MAC Record | MAC Record | MAC Record | MAC Record |